- 您现在的位置:买卖IC网 > Sheet目录2000 > IDTCV110NPVG (IDT, Integrated Device Technology Inc)IC FLEXPC CLK PROGR P4 56-SSOP

COMMERCIALTEMPERATURERANGE

IDTCV110N

PROGRAMMABLEFLEXPCCLOCKFORP4PROCESSOR

15

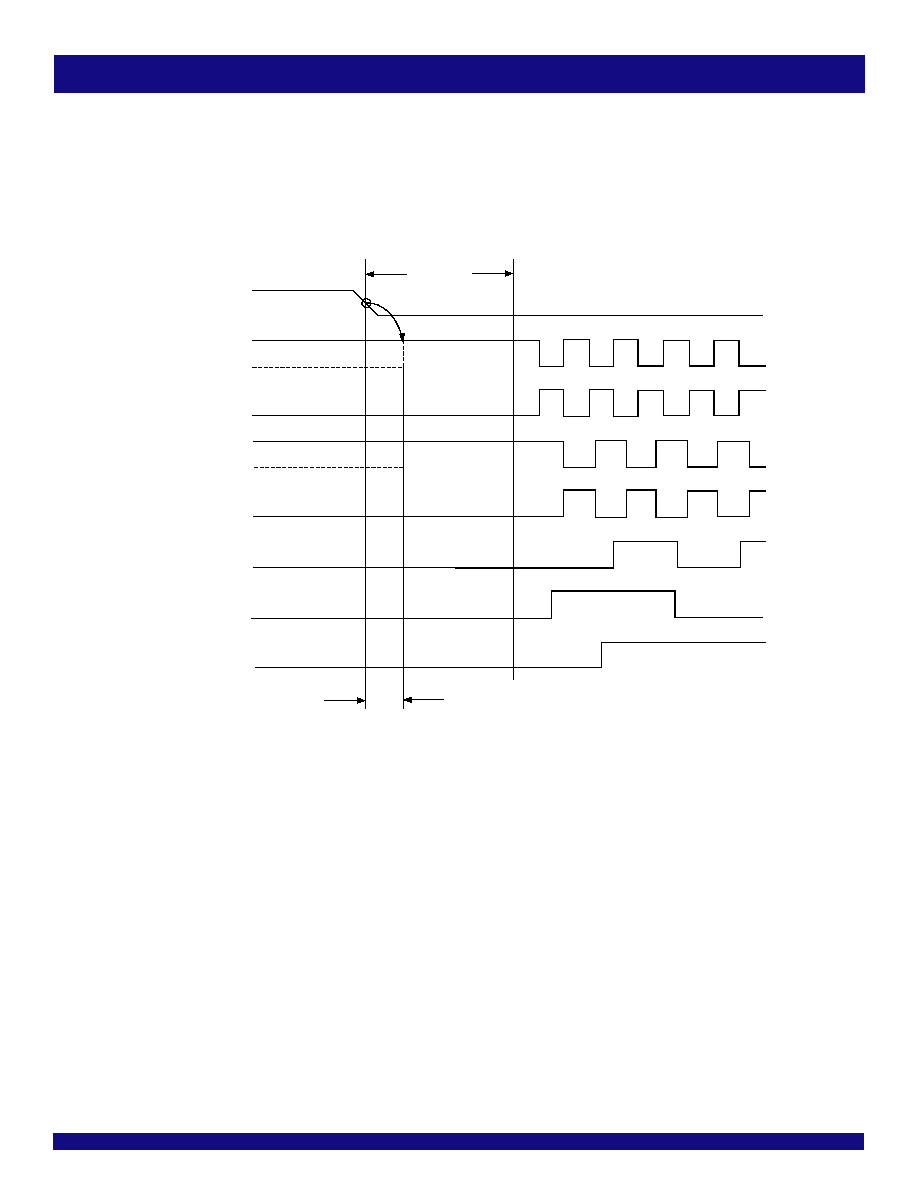

PD DE-ASSERTION

The time from the de-assertion of PD or until power supply ramps to get stable clocks will be less than 1.8ms. If the drive mode control bit for PD tristate is

programmed to ‘1’ the stopped differential pair must first be driven high to a minimum of 200mV in less than 300s of PD deassertion.

PD

CPU 133MHz

CPU# 133MHz

SRC 100MHz

SRC# 100MHz

USB 48MHz

PCI 33MHz

REF 14.31818

tSTAB <1.8mS

tDRIVE_PD

<300

μS, <200mV

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDTCV115-2PVG

IC FLEXPC CLK PROGR P4 56-TSSOP

IDTCV115FPVG

IC FLEXPC CLK PROGR P4 56-SSOP

IDTCV119EPVG8

IC CLK GEN DESKTOP PC 48-SSOP

IDTCV133PAG

IC FLEXPC CLK PROGR P4 56-TSSOP

IDTCV136PAG

IC FLEXPC CLK ATI RS400 56-TSSOP

IDTCV137PAG

IC FLEXPC CLK AMD K8 56-TSSOP

IDTCV142PAG

IC FLEXPC CLK PROGR P4 56-TSSOP

IDTCV146PVG

IC FLEXPC CLK PROGR P4 56-SSOP

相关代理商/技术参数

IDTCV110NPVG8

功能描述:IC FLEXPC CLK PROGR P4 56-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

IDTCV111IPAG

制造商:Integrated Device Technology Inc 功能描述:400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56

IDTCV115-2

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:PROGRAMMABLE FLEXPC? CLOCK FOR P4 PROCESSOR

IDTCV115-2PV

功能描述:IC FLEXPC CLK PROGR P4 56-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDTCV115-2PV8

功能描述:IC FLEXPC CLK PROGR P4 56-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDTCV115-2PVG

功能描述:IC FLEXPC CLK PROGR P4 56-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDTCV115-2PVG8

功能描述:IC FLEXPC CLK PROGR P4 56-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

IDTCV115-4PVG

功能描述:IC FLEXPC CLK PROGR P4 56-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT